System-level design of mixed-signal integrated circuits

Researchers at the Semiconductor Technology Academic Research Centre have developed a way to reduce the time it takes to design mixed-signal semiconductors by 50%.

In the competitive world of mixed-signal design, project delays are deadly for profitability. Design cycles are short, and the market moves very quickly, giving a competitive edge to any company that manages to accelerate its design process. At the Semiconductor Technology Academic Research Centre (STARC), we have been given the mission of finding a way to cut design time in half and eliminate costly respins for our supporting companies. We have achieved this goal with our new system-level design flow.

Our system-level design flow (which we call STARCAD-AMS) starts with rapid and extensive behavioural modelling in Simulink. Once we have a design that works at the system level, we generate C code from our Simulink models and import it into Cadence Virtuoso, where it is simulated using AMS Designer. We use our C code to verify the correctness of our circuit-level designs. We have benchmarked our STARCAD-AMS flow using a sigma-delta analog-to-digital converter (ADC) design. Our results show that design time is cut in half.

Mixed-signal design challenges

Combining analog and digital components on a single chip creates challenges not typically encountered in the design of strictly analog or strictly digital devices. First, the overall system design must be partitioned into its analog and digital parts. Most companies rely on the subjective judgement of the engineer to do this rather than basing partition decisions on practical implementation constraints, objectives and tangible metrics. Second, the disparate design environments used by system-level and circuit-level designers hamper collaboration between the two groups. Third, to understand and mitigate layout effects for analog components, the entire design must be simulated at the circuit level using a language such as SPICE. Circuit-level simulations take too long to be practical for testing new design ideas or considering what-if scenarios.

The consequences of not addressing these challenges are costly. A survey of our member companies revealed that, on average, three respins are required to complete a new type of mixed-signal design. In addition to the financial cost of each respin, the resulting delays can render the design obsolete before it is even shipped.

The STARCAD-AMS design flow

In the first phase of the project, we focused on using layout tools, SPICE and other circuit-level simulators to improve the analog design process. Although we reduced design time by about 20%, many errors were still not caught until post-layout verification. These errors forced us to modify the original design and redo much of the work we had already completed.

To identify errors earlier, we shifted our focus from schematic to layout design. We then achieved an additional 50% reduction in design time. After that, we needed to shift our focus to system-level design for more effective mixed-signal design. After comparing various system-level design tools, we selected MATLAB and Simulink, as we knew that with MATLAB and Simulink we would be able to run fast simulations. Code generated from Simulink models can be integrated with Cadence and our circuit-level design flow - a key requirement.

In the STARCAD-AMS flow, we codesign and model the analog and digital parts of the device in Simulink and then run system-level simulations to analyse the behaviour and performance of design alternatives under a variety of operating conditions. For example, we study how the signal-to-noise ratio is affected by the signal bandwidth and by variations in the power supply signal. We also evaluate the effect of component changes; for example, we determine how op amp and comparator parameters affect overall system performance.

Understanding complex system relationships such as these is essential to design optimisation. By using Simulink instead of a circuit-level simulator, we can complete hundreds of simulations in the time it previously took to complete one.

Once we have verified the behaviour of the design in Simulink, we generate C code from the model using Simulink Coder and Embedded Coder. We import the C code into Cadence Virtuoso and simulate it within a circuit-level model using AMS Designer. By comparing Simulink simulation results with AMS Designer simulation results, we verify the circuit-level model. For the digital parts of the design, we first verify each component, then groups of components, and finally, the entire system. For the analog parts, verification begins with groups of analog components. The design process then continues into the circuit-level flow we established in the early stages of STARCAD-AMS development.

The STARCAD-AMS workflow facilitates design partitioning because it enables a rapid transition from the system model to a register transfer level (RTL) design, logic synthesis and a netlist. From the netlist, engineers can estimate the area and power requirements of the circuit and make informed decisions about optimal partitioning.

In addition to analog and digital component modelling, we used Simulink to create test benches. In this use case, the C code generated from Simulink is used to drive input signals in a circuit-level simulation.

Designing a sigma-delta analog-to-digital converter

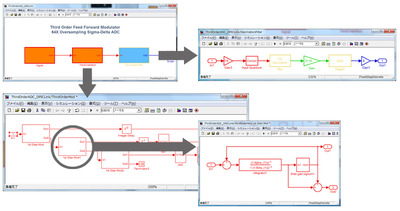

To test the new workflow, we applied it to the design of a third-order, sigma-delta ADC. The modulator and decimation filter were modelled in Simulink using integrator, gain and filter blocks, as well as transfer function blocks and MATLAB Function blocks (Figure 1). The complete design included approximately 200 analog elements and 200 digital gates.

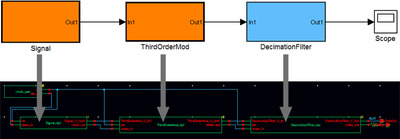

After modelling and simulating the initial design, we used MATLAB scripts to programmatically adjust system parameters in the model. Next, we generated C code from the model and imported the code into AMS Designer (Figure 2).

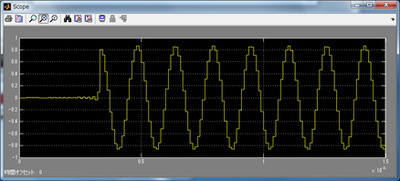

We ran simulations in AMS Designer using the same input signals and compared the AMS Designer output with the Simulink output to verify the AMS Designer implementation (Figure 3).

Using the STARCAD-AMS analog-digital codesign flow, our objective is to reduce design time by half. The third-order ADC took three engineer-days from system design to post-layout verification. When the same system was designed by another team using Verilog-AMS, this effort required six engineer-days. We estimate that the same design would have taken two months using only circuit-level design and simulation tools.

Ongoing development

We have demonstrated STARCAD-AMS to our member companies. Engineers at those companies will use the new flow on more complex mixed-signal designs, such as deserialisers (SERDES), phase-locked loops (PLLs) and digital pre-distortion (DPD) devices. We continue to improve STARCAD-AMS and plan to further automate the entire process from system-level design to schematics and mask data.

Where industry meets: RFUANZ and Comms Connect 2026

RFUANZ looks forward to engaging with members in Wellington and continuing the conversation on...

ARCIA update: news from the Mobile World Congress and IWCE

Mobile World Congress is the showcase for global telecommunications, with over 100,000 visitors,...

Comms Connect NZ to feature a ministerial welcome

The Southern Hemisphere's premier critical communications and public safety event, Comms...